### Master's Thesis in Computer Science

# Combining the DKU Pattern with Polyhedral Optimization and Tiling

by Stefan Kronawitter

Supervisor: Dr. Armin Größlinger Examiner: Prof. Christian Lengauer, Ph.D.

April 30, 2013

#### Abstract

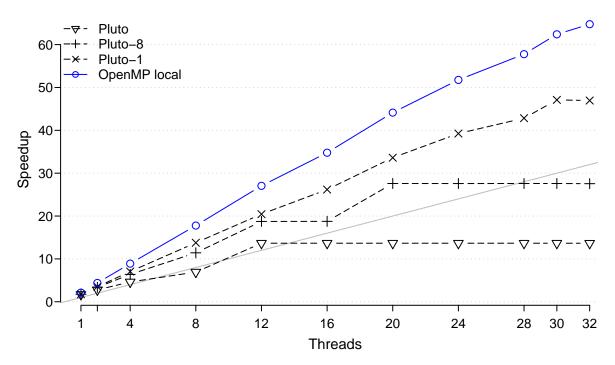

Performance portability is a huge problem when parallelizing an application. Practically, the source codes for parallel systems are strongly adapted to the available hardware and therefore the performance of the application is tightly coupled to a single machine. This dependency can be weakened by transferring the necessity for strong adaptions from the application code to a framework, which acts as an additional layer between the user application and the hardware. Moving to a new system then only requires the adaption of a single framework and leave all other source code untouched.

For application codes fitting the polyhedron model, this thesis introduces a new way to generate automatically the program code specific for a parallelization framework. A generator was developed, which only requires a sequential version of the application code to create architecture independent methods required by the framework in order to execute the application in parallel. The generated code is also able to exploit the communication required on distributed memory systems in order to apply layout optimizations, which leads to an additional speedup on top of the parallelization itself.

#### Acknowledgements

This work would not have been possible without the support of many people.

First of all, I would like to thank my advisior Armin Größlinger for his help during all stages of this work; starting from the first decisions for the implementation until the proofreading for this work. No matter if I had problems concerning the development of the DKU generator, or if I needed help to understand the behaviour of the generated code, he had always time to answer my questions.

I am also very grateful to Christian Lengauer, who gave me the time and opportunity to finish this work, although the next project I am participating in already started.

Especially I want to thank Sean Halle for providing me his implementation of the DKU framework, on which this work is based.

In addition, I would like to thank my office mate Andreas Simbürger for his help in every situation and the proofreading of many chapters. Thanks also to all colleagues within LooPo for many very fruitful discussions concerning my master's thesis and the humorous private conversations in between.

Beside all support concerning this work, I want to thank my family and all my friends, who provided me the motivation for not only this work, but also for the whole studies on the one side, and the distance and regeneration on the other side.

## Contents

| 1  | Intro        | oduction                      | 7  |  |

|----|--------------|-------------------------------|----|--|

| 2  | Background   |                               |    |  |

|    | 2.1          | Polyhedron Model              | 9  |  |

|    | 2.2          | Integer Set Library           | 11 |  |

|    | 2.3          | Polyhedral Extraction Tool    | 13 |  |

|    | 2.4          | Chunky Loop Generator         | 15 |  |

|    | 2.5          | DKU Pattern                   | 16 |  |

| 3  | Overview     |                               |    |  |

|    | 3.1          | Generator                     | 21 |  |

|    | 3.2          | DKU Framework                 | 24 |  |

| 4  | DKL          | J Framework                   | 27 |  |

| 5  | Generator    |                               |    |  |

|    | 5.1          | Input Description             | 31 |  |

|    | 5.2          | Polyhedral Optimizations      | 33 |  |

|    | 5.3          | Layout Transformation         | 38 |  |

|    | 5.4          | Code Generation               | 40 |  |

| 6  | Experiments  |                               |    |  |

|    | 6.1          | Available Hardware            | 51 |  |

|    | 6.2          | Problems and Paradox Behavior | 51 |  |

|    | 6.3          | Preparations                  | 55 |  |

|    | 6.4          | Evaluation                    | 59 |  |

|    | 6.5          | Comparison with Pluto         | 71 |  |

| 7  | 7 Conclusion |                               | 81 |  |

| Bi | Bibliography |                               |    |  |

## **1** Introduction

One of the first decisions when parallelizing an application is to choose a programming language. If the target hardware uses shared memory, OpenMP can be a good choice. But OpenMP is not able to handle communication between different nodes on a cluster. So, for best performance on varying hardware, the algorithm must be ported to different parallel languages and, in practice, it is also closely adapted to a single target machine. In this case, the so-called performance portability problem appears every time the hardware changes.

One solution for this dilemma would be to use an automatic parallelization tool and/or a parallelizing compiler. But such a tool or compiler will be very complex, if it has to generate code suitable to the large number of architectures available.

Another approach is to use a framework as an additional layer between the application code and the parallel hardware, which encapsulates the choice of the used parallel languages and paradigms that fits best to the used machine. Based on this, the programmer has to provide a more abstract and architecture independent code using a special pattern, whereas the framework is the only part which is completely adapted to the actual hardware. When moving to another machine, none of the application codes need to be touched, only the framework must be ported and optimized again.

Given such a framework, a next possible step is to generate the application code for the framework automatically, starting with a simple sequential version. This part – the code generation for the framework based on the polyhedron model – is the main task of this thesis. Such a parallelization framework requires specific methods for, e.g., preparing the input to communicate all required data to the nodes, or to divide the computation in order to execute it in parallel. This information can be computed completely automatically, if the application code can be represented using the polyhedron model.

Therefore, a generator was developed, which only takes a sequential version or a polyhedron description of the application code and automatically generates all required methods for a parallelization framework. Chapter 2 provides a brief introduction into the used libraries, the DKU pattern for the parallelization framework and the polyhedron model, which is used by the generator to perform all transformations and optimizations in. An overview over the usage of both the generator and the DKU framework is given in Chapter 3, while Chapters 4 and 5 describe the internals of both in more detail. Chapter 6 presents and explains some strange effects that appeared during the implementation and testing of the generator. The performance achieved, when using the automatically generated application code with the DKU framework, is also discussed in this chapter. Finally, Chapter 7 summarizes the results and discusses future work.

### 2 Background

#### 2.1 Polyhedron Model

Many techniques used to optimize and parallelize loop nests modify the source code of the loop structure. Different and more powerful approaches are based on mathematical models and therefore, they do not need the textual structure of the source code. The polyhedron model [FL11] serves as an abstract representation of a loop program. The first usage of this model in a loop parallelization context was presented by Lengauer in 1993 [Len93]. In contrast to previous loop parallelization techniques, it is based on a mathematical model using polyhedra. This allows more powerful transformations than text-based approaches and it has evolved even further since then.

Unlike other models, such as abstract syntax trees, its basic component is a statement instance, i.e., one specific execution of a statement. Each instance is represented by a node in the computation graph, which is associated with a point  $\vec{i} \in \mathbb{Z}^d$ . The components of this so-called iteration vector correspond to the values of the iterator variables of the *d* loops surrounding the statement this instance belongs to. The vector  $\vec{i}$  is also the position of the statement instance in the computation graph.

In addition to the loop variables, the model also contains structure parameters, which typically correspond to the problem size. For example the numbers of rows and columns for both input arrays of a matrix multiplication are denoted by structure parameters. They are unknown at compile time, as the size typically varies for different invocations, but they are constant at run time.

If each loop bound of a loop nest is an affine inequation in the surrounding loop variables and structure parameters, the set of instances depicts a  $\mathbb{Z}$ -polyhedron, the so called iteration domain of the loop program. A  $\mathbb{Z}$ -polyhedron is the intersection of a (rational) polyhedron with  $\mathbb{Z}^d$  or a lattice, so it contains only integral points. This enables a compact representation, which is independent from the number of loop iterations or the runtime values for the structure parameters.

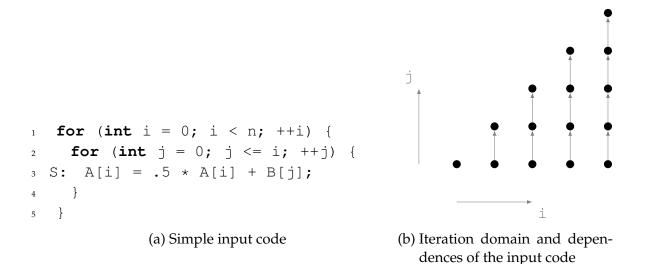

Figure 2.1: Polyhedron model of a simple loop nest

Consider the source code of Figure 2.1a. The loop program consists of a single statement S which is enclosed by two loops and its iteration vector is therefore  $\vec{i} = (i, j)^{T}$ . According to the loop bounds the iteration domain of this statement is defined by the constraints

$0 \leq \texttt{i} < \texttt{n}, \ 0 \leq \texttt{j} \leq \texttt{i},$

where *n* is a constant structure parameter. The computation graph of this iteration domain for n = 5 is depicted in Figure 2.1b.

In addition to the iteration domain, the execution order of the statement instances must also be specified for a complete and well-defined model of the input program. As a statement instance cannot be executed before itself, the ordering must be strict and it is represented as directed edges in the computation graph. In the case of a sequential program, every pair of different instances can be ordered, which leads to a total ordering. If the loop nest should be executed in parallel, the total ordering must be replaced by a partial one, as two parallel instructions can be executed in an arbitrary ordering, or completely simultaneously.

This leads to the new problem of finding an appropriate ordering, which has enough parallelism to utilize as much parallel execution units as possible without changing the result of the loop nest. A common approach to deal with this is to use the dependences between the instances which was first formulated by Bernstein [Ber66]. **Definition 1 (Dependence)** *Two different instances u and v are said to be in dependence iff both access the same memory cell and at least one of them modifies it.*

Therefore, if *u* and *v* are executed in the same sequence as given by the initial total ordering, their result is guaranteed to be identical with the sequential version. Utilizing this, the orderding deduced by the dependencies of the statement instances along with the original iteration domain describe a parallel program that leads to the same result as the sequential version.

Consider again the loop code of Figure 2.1a. The array elements A[i] are updateded for each value of j, i.e. they depend on the old value and therefore all modifications of one sepcific array cell must not be interchanged. In particular, all instances with the same value for i are in dependence. According to the original, sequential version, every instance  $(i, j)^{T}$  depends on and must be executed after the instance  $(i, j-1)^{T}$ , if it exists. Although the elements of the array B are also accessed multiple times, this need not be considered here as there is no write access to B. The dependences are also shown in Figure 2.1b.

As long as both loop bounds and array subscripts are affine relations in the loop variables and additional structure parameters, all dependencies can be efficiently computed using integer linear programming tools [Fea91].

In contrast to work directly with a relation representing the ordering for the program, it is more handy to use a mapping from the iteration domain to a multidimensional virtual time  $\mathbb{Z}^t$  for an arbitrary t. The idea of this mapping is to transform the iteration domain in a way such that the resulting virtual time is totally ordered using the lexicographical ordering  $<_{lex}$ . For all  $\vec{a}, \vec{b} \in \mathbb{Z}^t$  the following equivalence holds:

$$\vec{a} <_{lex} \vec{b} \iff \exists m \ge 0 : \forall i < m : a_i = b_i \land a_m < b_m.$$

Such a mapping is called a schedule for a given statement. A valid parallel schedule for the example of Figure 2.1 is  $(i, j)^{\top} \rightarrow j$ , as all values for i can be executed simultaneously and the j-loop must remain sequential.

#### 2.2 Integer Set Library

The Integer Set Library (isl) [Ver10] is today one of the most frequently used C libraries when working with the polyhedron model. It can efficiently handle integer sets and relations bounded by affine inequalities. Operations for manipulating them are for example set/map union, intersection, or coalescing.

The library is also able to deal with unknown but constant parameters and existentially quantified variables. The latter are e.g. used to model holes in a  $\mathbb{Z}$ polyhedron. Consider for example the simple loop:

```

for (int i = 0; i < n; i += 2)

T: A[i] = 0;</pre>

```

A first attempt to model the iteration domain of statement T is with the constraint  $0 \le i < n$ , but this covers odd values for i, too. Actually it is not possible to describe the iteration domain of this example without any extensions to the model. To deal with this, isl uses existentially quantified variables, which do not modify the shape of the polyhedron, but the integral points inside it. A valid iteration domain can then be represented by the constraints:  $0 \le i < n \land \exists a \in \mathbb{Z}$ :  $2 \cdot a = i$ .

Back to the example of Figure 2.1, the iteration domain of statement S can be written in isl syntax as follows:

```

[n] -> { S[i, j] : 0 <= i and i < n and 0 <= j and j <= i }

```

In this example, n is a structure parameter which denotes the size of both arrays. In isl syntax, structure parameters of a set are placed in front of it. Sets can also be named, which is done by adding a label before the domain vector. In the given example, the tuple is named "S".

Relations are denoted very similiar in isl. The only difference is that there is not only a domain vector, but also a range vector in front of the constraints. Both vectors may be labeled and they are connected by an ASCII arrow. The schedule for the given code of Figure 2.1a can be denoted in isl syntax as follows:

[n] -> { S[i, j] -> [i, j] }

In addition to some basic methods to inspect and manipulate sets or maps, isl also offers higher level functions used in loop/compiler optimization like performing a dependence analysis or computing an optimal schedule for the given constraints. As all computations are performed with GMP [Gt12], the library can deal with arbitrary sized integers.

isl provides access to extended functionality through the use of other libraries, e.g. barvinok, a library for counting the number of integer points in a polyhedron, or the iscc calculator, which provides an easy to use interface due to its very high abstraction level.

```

[n] -> { S[i, j] : j <= i and i <= -1 + n and j >= 0 }

1

[n] -> { S[i, j] -> [0, i, 0, j, 0] }

3

[n] -> { S[i, j] -> A[i] }

4

read: 0

5

write: 1

6

+

7

*

8

0.5

9

[n] -> { S[i, j] -> A[i] }

10

read: 1

11

write: 0

12

[n] -> { S[i, j] -> B[j] }

13

read: 1

14

write: 0

15

```

Figure 2.2: Model of statement S from Figure 2.1a, extracted with pet.

#### 2.3 Polyhedral Extraction Tool

The Polyhedral Extraction Tool (pet) [VG12] is designed to extract a polyhedral representation from C source code. In contrast to other tools, pet does not have its own C parser. It uses LLVM's C frontend clang instead and the polyhedral description is extracted directly from the high-level abstract syntax tree. This grants pet full support of C99 and, therefore, it can deal with, e.g., variable-length arrays. The user can also benefit from the very nice warnings and error messages that clang generates.

The extracted polyhedral representation is stored by the isl (cf. Section 2.2). For each statement, pet returns an abstract syntax tree of the statement's code along with the corresponding iteration domain and schedule. Additionally all array accesses are represented by a mapping from the iteration domain to the actual index and the type of the access, which denotes if it as a read or write access (or both). Therefore, transformations of the access relations are also possible, which reduces the effort of, e.g., memory layout optimizations.

Consider again the sample code of Figure 2.1a, the extracted representation of statement S is shown in Figure 2.2. The first line shows the iteration domain and is identical to the representation shown in Section 2.2. (The missing constraint 0 < i can be deduced from 0 < j and j <= i and is therefore not needed.) Line 2

1 for (int i = ...)

2 for (int j = ...)

2 [0, i, j];

3 S(i, j);

T[i, j] -> [1, i, j];

4 for (int i = ...)

5 for (int j = ...)

6 T(i, j);

(a) Constant output dimension in first position.

1 for (int i = ...) {

2 for (int j = ...)

S[i, j] -> [i, 0, j];

T[i, j] -> [i, 1, j];

4 for (int j = ...)

5 T(i, j);

6 }

(b) Constant output dimension between others.

1 for (int i = ...) {

2 for (int j = ...) {

2 for (int j = ...) {

3 S[i, j] -> [i, j, 0]; 3 S(i, j);

T[i, j] -> [i, j, 1]; 4 T(i, j);

5 }

6 }

6 }

(c) Constant output dimension in last position.

Figure 2.3: Effect of additional constant output dimensions for the schedule.

contains the schedule for statement S. As the surrounding loops scan the iteration domain in a lexicographic order, the schedule can be an identity map.

In a general situation of more than one statement, the schedule must not only specify the ordering of the instances for each statement separately but also between all statements. An easy way to achieve this is to add additional output dimensions to the schedule mapping. Consider the examples of Figure 2.3, as the instances are scanned in a lexicographic ordering after applying the schedule map to the iteration domain, different values of an additional constant dimension can be seen as different loop nests for the following inner loops.

The last lines of Figure 2.2 define the structure of the statement using an abstract syntax tree and, as already mentioned, array accesses are represented by an isl map.

```

1 #define S(i,j) A[i] = .5 * A[i] + B[j]

2

3 for (c2=0;c2<=n-1;c2++) {

4 for (c4=0;c4<=c2;c4++) {

5 S(c2,c4);

6 }

7 }</pre>

```

Figure 2.4: Loop code generated by CLooG using the model from Figure 2.2.

### 2.4 Chunky Loop Generator

*CLooG* is a tool to generate loop code for scanning integer polyhedra [Bas04]. Originally it was designed to resolve the loop generation problem, which was one of the main challenges for compilers when using the polyhedron model. That is, previously known algorithms for generating target code either require severe restrictions on the schedule, which limits the possibility for optimizations, or they are simply too expensive to be included in real-life compilers. Beside preventing these problems, the generated code is also trimmed for efficiency, i.e., control overhead is avoided wherever possible. Therefore, CLooG does not create a loop with only one iteration (if this can be determined statically) and, in general, it can completely unroll loops with only few iterations. The resulting code is also valid C code, assuming methods or preprocessor definitions for min, max, floord, and ceild are available.

Lines 3 – 7 in Figure 2.4 show the generated C code when running CLooG with the model from Figure 2.2. CLooG does not know the actual code for the statement, so it adds a call to the statement label. The parameters for this invokation are specified by the iteration domain and any transformation given by the schedule is revoked, i.e. if for example the schedule interchanges both loops (e.g. with  $[n] \rightarrow \{ S[i, j] \rightarrow [0, j, 0, i, 0] \}$ ) the corresponding call in the generated code would be S(c4, c2);.

As already mentioned the statement code must be inserted manually, which can be easily accomplished by using a preprocessor macro as depicted in the first line of Figure 2.4. This works fine, if the macro inserts only a single statement, but in more complex situations, it can lead to invalid C code; encapsulating the statements in a do  $\{ \ldots \}$  while(0) block is more fail-safe and should be preferred when automatically generating code.

#### 2.5 DKU Pattern

DKU is the short form for "Divider, Kernel, Undivider", which is the the core part of this pattern [HC09]. As the name suggests, it is a variant of a divide and conquer approach. The programmer has to provide equally named methods for these routines, so the framework is able to encapsulate the code concerning parallelism and all related constructs to deal with performance portability problem. Therefore, the main idea of this pattern is to adapt only the framework to the actual hardware and to keep the application code untouched. That is, when updating the hardware or even when switching to a new architecture only the framework has to be ported and all application code can be reused.

In DKU, computations are represented as *pieces* where each piece contains a user pointer to access all required application specific data, including all information about its computation size. All user methods provided to the framework operate on these.

The divider's task is to split the given piece in a set of disjoint, (ideally) equally sized subpieces, concerning the work load of the computation. The desired number of subpieces is passed along with the piece itself to the user method. The only constraint is that the generated subpieces define computations with no dependencies in between, i.e. with no synchronization or any need for communication.

After splitting the computation using the divider, the kernel is called once for each generated subpiece. Each of them is computed by one thread, so the user code for the kernel should be purely sequential. Therefore, the programmer does not need to know anything about parallel constructs like OpenMP<sup>1</sup> or MPI<sup>2</sup>. The parallelization part is completely hidden within the framework.

Each kernel computes one part of the result and the undivider must ensure the root piece contains the whole result at the end. Therefore, the undivider is called once for each subpiece and its input is the subpiece itself and its corresponding parent. Both pieces are allowed to share the same memory area for the result, so in this case the programmer may provide an empty undivider. (Disregarding the memory management.)

Figure 2.5 shows a complete example of how the DKU Pattern can be used to parallelize a matrix multiplication.

<sup>&</sup>lt;sup>1</sup> Open Multiprocessing (http://openmp.org/wp/)

<sup>&</sup>lt;sup>2</sup> Message Passing Interface (https://www.mcs.anl.gov/research/projects/mpi/)

```

1 struct Matrices {

int acRows, bcCols, aCols bRows;

2

int cBeginRow, cEndRow, cBeginCol, cEndCol; // cEndRow and Col exclusive

3

float *A, *B, *C;

4

};

5

6

void Divider(struct DKU Piece *p, int n,

7

struct DKU_Piece **sub_ps, int *nr_sub_ps) {

8

// find largest m \leq n such that m = 2^b for a natural b

9

int b = 0;

10

while ((n >>= 1) > 0) ++b;

11

*nr_sub_ps = 1 << b;

12

13

struct Matrices *mats = p->user;

14

int cRowLen = mats->cEndRow - mats->cBeginRow;

15

int cColLen = mats->cEndCol - mats->cBeginCol;

16

17

int x = 1 \ll (b/2), y = (1 \ll b) / x;

18

for (int i = 0; i < x; ++i)</pre>

19

for (int j = 0; j < y; ++j) {

20

*sub_ps = DKU_Piece_alloc();

21

struct Matrices *sub_mats = (*sub_ps)->user = malloc(sizeof(mats));

22

sub_ps++;

23

memcpy(sub_mats, mats, sizeof(struct Matrices));

24

25

sub_mats->cBeginRow += i * cRowLen / x;

26

sub_mats->cEndRow = sub_mats->cBeginRow + cRowLen / x;

27

sub_mats->cBeginCol += j * cColLen / y;

28

sub_mats->cEndCol = sub_mats->cBeginCol + cColLen / y;

29

}

30

31

}

32

void Kernel(struct DKU_Piece *p) {

33

struct Matrices *mats = p->user;

34

float *A = mats->A, *B = mats->B, *C = mats->C;

35

int acRows = mats->acRows, bRows = mats->aCols_bRows;

36

37

38

for (int i = mats->cBeginRow; i < mats->cEndRow; ++i)

for (int j = mats->cBeginCol; i < mats->cEndCol; ++j)

39

for (int k = 0; k < mats->aCols_bRows; ++k)

40

C[i * acRows + j] += A[i * acRows + k] * B[k * bRows + k];

41

42

}

43

void Undivider(struct DKU_Piece *p, struct DKU_Piece *sub) {

44

free(sub->user);

45

DKU_Piece_free(sub);

46

47 }

```

Figure 2.5: Simple example for the methods the user has to provide to compute the matrix multiplication with DKU. (Assuming matrix C can be divided without any remainder.)

```

void schedule(struct DKU Piece *p) {

1

struct DKU_Piece *sub_ps[nr_cpus];

2

int nr_sub_ps;

3

4

Divider(p, nr_cpus, &sub_ps, &nr_sub_ps);

5

#pragma omp parallel for

7

for (int i = 0; i < p->nr_sub_ps; ++i) {

8

Kernel(sub_ps[i]);

9

Undivider(p, sub_ps[i]);

10

}

11

}

12

```

Figure 2.6: Simple OpenMP scheduler for a DKU framework.

As a DKU\_Piece can hold exactly one pointer for the whole user data, the first part is the definition of a structure to encapsulate all data, which is needed by the user methods.

The most complicated method is the divider. Its task is to divide the computation optimally. In a standard matrix multiplication, all elements of the result matrix can be computed independently and, therefore, both loops iterating over either the rows or the columns of this matrix can be split. If the divider is asked to generate n subpieces, it has to find two natural numbers  $x, y \in \mathbb{N}$  such that  $x \cdot y$  is close to n. For the sake of convenience, the shown divider uses a quite simple heuristic to compute these values, assuming n is a power of 2.

The next method presented is the kernel. It extracts relevant data from the piece and then computes the result for the specified part of the computation, which is in this example a submatrix of C. It can be easily seen that all pieces can be computed simultaneously by invoking the kernel multiple times in parallel.

The last method needed is the undivider. As all pieces share the same memory location for the result matrix, the undivider need not collect any data. Only memory management is left for this method.

Figure 2.6 shows a small scheduler for a DKU framework. After dividing the input the subpleces are executed by multiple OpenMP threads on a shared memory architecture.

An extension to distributed memory systems is a bit more complex and requires the programmer to provide four additional methods, namely BundleInput, UnbundleInput, BundleResult, and UnbundleResult. Distributed memory architectures require data transfer for both input and result. In case of MPI, the communication must be performed explicitly by the scheduler and therefore both input and result must be bundled before and unbundled after the transfer. As the framework itself does not know anything about the actual user data, this part has to be done by the user.

An extension to the aforementioned matrix multiplication example can be seen in Figure 2.7. The BundleInput method first computes the space for the whole input and copies all data to the newly allocated memory. As the kernel requires only a part of the input matrices, an obvious optimization would be to store submatrices of A and B in the generated bundle to reduce the communication overhead, but for lack of space and a better comprehensibility the complete matrices are copied here. The scheduler is then able to transfer the bundle to another node, which can restore the input using the UnbundleInput method. After invoking the kernel, the result must be bundled again using BundleResult and communicated back to the master, which uses the UnbundleResult method to merge all parts of the result. The result bundle can be optimized again by only transferring the computed submatrix and not the whole C.

```

void BundleInput(struct DKU_Piece *p, void **bundle, int *size) {

struct Matrices *mats = p->user;

2

int sizeA = mats->acRows * mats->aCols_bRows * sizeof(float);

3

int sizeB = mats->aCols_bRows * mats->bcCols * sizeof(float);

4

*size = 7 * sizeof(int) + sizeA + sizeB;

5

6

*bundle = malloc(*size); int *b int = *bundle;

7

b_int[0] = acRows; b_int[1] = bcCols; b_int[2] = aCols_bRows;

8

b_int[3] = cBeginRow; b_int[4] = cEndRow;

9

b_int[5] = cBeginCol; b_int[6] = cEndCol;

10

11

char *b_char = (char *) (b_int + 7);

12

memcpy(b_char, mats->A, sizeA); b_char += sizeA;

13

memcpy(b_char, mats->B, sizeB);

14

15

}

16

void UnbundleInput(void *bundle, int size, struct DKU_Piece *p) {

17

struct Matrices *mats = p->user = malloc(sizeof(struct Matrices));

18

int *b_int = bundle;

19

mats->acRows = b_int[0]; mats->bcCols = b_int[1];

20

mats->aCols_bRows = b_int[2];

21

mats->cBeginRow = b_int[3]; mats->cEndRow = b_int[4];

22

mats->cBeginCol = b_int[5]; mats->cEndCol = b_int[6];

23

24

int lenA = mats->acRows * mats->aCols bRows;

25

int lenB = mats->aCols_bRows * mats->bcCols;

26

int lenC = mats->acRows * mats->bcCols;

27

28

mats \rightarrow A = (float *) (b_int + 7);

29

mats->B = mats->A + lenA;

30

mats->C = malloc(lenC * sizeof(float));

31

32 }

33

34 void BundleResult(struct DKU_Piece *p, void **bundle, int *size) {

struct Matrices *mats = p->user;

35

*size = mats->acRows * mats->bcCols * sizeof(float); // only C needed

36

*bundle = malloc(*size);

37

38

memcpy(*bundle, mats->C, *size);

free(mats->C);

39

40 }

41

42 void UnbundleResult(void *bundle, int size, struct DKU_Piece *p) {

struct Matrices *mats = p->user;

43

float *res = bundle;

44

for (int i = mats->cBeginRow; i < mats->cEndRow; ++i)

45

for (int j = mats->cBeginCol; i < mats->cEndCol; ++j)

46

mats->C[i * mats->acRows + j] = res[i * mats->acRows + j];

47

48

}

```

### Figure 2.7: Bundle and unbundling methods for the matrix multiplication example of Figure 2.5.

### **3** Overview

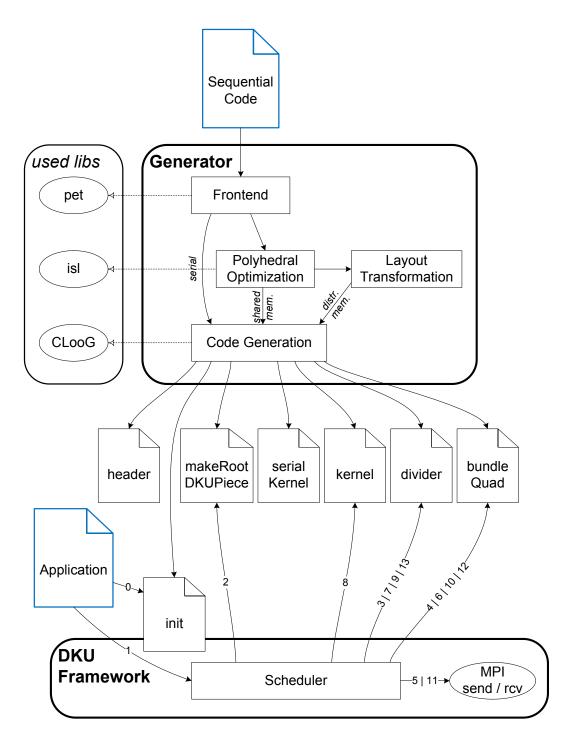

This chapter provides a brief overview of the procedure and the data flow when implementing a new program with the DKU framework using the generator. The simplified process is shown in Figure 3.1.

#### 3.1 Generator

**Frontend** The generator takes two input files:

- a C99 source file, containing the application kernel code,

- a desired memory layout transformations in isl syntax (optional).

The first obligatory input is a source file, which contains a sequential version of the loop program that should be executed in parallel using the DKU framework. As the input file is parsed by LLVM's C-frontend clang, the input must be a valid C99 file. Simplifications for the input, which are not specified by the standard, such as writing only the loop nest and omitting the method signature, are not permitted. In order to specify which part of the input code should be considered, the loop nest must be surrounded by #pragma scop and #pragma endscop. Variables have to be defined outside this block, apart from the loop iterator definitions in the header of for loops.

Beside the input code for the algorithm itself, the user is allowed to pass another file containing only an isl map in isl syntax, which represents a layout transformation for the used arrays. If no transformation is needed, the parameter for the frontend can be omitted, or an empty map, denoted by {}, may be passed. As the bundling methods need to copy the arrays anyway, it is easily possible to change their layout here in order to improve the performance of the kernel code. But on a shared memory system, it may be sufficient to simply divide the input and start the actual computation without any communication overhead. Therefore neither of the bundle methods is invoked and the used kernel must be able to deal with

Figure 3.1: Simplified process when using the DKU framework along with the generator. Blue files denote user written code, oval shapes are external libraries.

the original array layout. This enforces the generator to create two different kernel methods, because a layout transformation may change the type of an input array, e.g. when transposing a rectangular, non-squared matrix, but C requires the types of variables to be fixed not later than at compile time.

The extracted polyhedral representation of the input code mainly consists of two parts:

- one array, that contains all used arrays of the input code and

- another array, that holds all statements of the loop nest.

Each statement contains its iteration domain and schedule. The first is represented by an isl set, the latter by an isl map. The actual statement code is represented by an abstract syntax tree, which contains isl maps to represent array accesses. These relations map from the iteration domain to the index vector, which is used to access the memory. The extracted polyhedral description is then transformed to the input for the generator, which is close to the data structure pet returns. A more detailed description of the input can be found in Section 5.1.

**Optimizations** The next task that the generator executes contains polyhedral optimizations, as depicted in Figure 3.1. The generator uses isl to perform a dependence analysis on the representation. The results are then used to compute an optimal schedule utilizing the built-in scheduler of isl. Based on this schedule, a new iteration domain and a new schedule for the kernel code must be created, which cover only a subset of the original iteration domain. In order to delimit the domain of the isl set, new parameters for the loop bounds have to be introduced. Section 5.2 provides more information about the polyhedral optimizations, that are performed.

An additional part is to apply the layout transformations for all used arrays. This implies to modify the statements itself and also to adjust the bundle methods to ensure they perform the transformations when creating the input bundle and to revert the layout transformation, when collecting all results. A new idea of how to automatically compute a suitable layout transformation is presented in Section 5.3.

**Code Generation** All computed information is then used to create the source code for the DKU framework. During this process, the polyhedral code generator CLooG is invoked multiple times. The following files are generated here:

- **header** The first one created is the header for the application. It contains declarations for all methods of the following files and two structure definitions. One to encapsulate all user data and another for management information added by the generator and needed by the following files.

- **init** The initializer introduces all user methods to the framework. Therefore, it has to be invoked before executing the scheduler.

- **makeRootDKUPieces** This file contains an equally named method that allocates the first DKU piece based on the user data passed to it.

- **serialKernel** This file contains a fall-back solution for the kernel if only one processor is available. The loop code is generated directly with CLooG using the input model without any transformation or optimization.

- **kernel** Contains two kernel methods: one using the original memory layout, the localKernel, and one using the optimized layout, the kernel. Analogous to the serial kernel, the loop nest for the application is generated by CLooG's pretty printer.

- **divider** This file contains the methods divide and undivide. The divider is organized in a way such that all pieces share the same memory for the data. The undivider only need to free the data structure for the piece.

- bundleQuad Contains four bundling methods: bundleInput, unbundleInput, bundleResult and unbundleResult, can be found in this file. The loop code to copy from or into the bundle memory is also generated by CLooG.

More information on how these methods are generated can be found in Section 5.4.

#### 3.2 DKU Framework

**Initialization** After all DKU methods are created, the user is able to call the initializer and the scheduler in order to start the computation (c.f. to edges 0 and 1 from Figure 3.1).

A first, architecture-independent step is to create the root pieces for the framework. Therefore, the user method makeDKUPieces is invoked (2), which is in general allowed to create more then one root piece. They are used to specify and start several independent computations at once. But as the user code is generated automatically for exactly one given loop nest by the described generator, this method only returns a single root piece. However, an extension of the generator, that allows building more than one root piece is possible.

For parallel systems there are two different architectures that should be discussed here: distributed and shared memory systems.

**General Procedure for Distributed Memory** When using any kind of distributed memory system, the scheduler divides the given piece into as many subpieces as nodes are available in the network (3). Each subpiece is then bundled using the bundleInput method (4), which performs a layout transformation to enhance the cache utilization for the kernel. The created memory blocks are transferred to the corresponding nodes using explicit MPI sends (5) and the receivers restore their piece utilizing the unbundleInput method (6). Every node invokes the divider again to generate pieces for each CPU core (7). Bundling is not necessary for distributing pieces to cores as the cores of each node have shared memory. It is also possible to generate more subpieces than computing units are available to reduce the computational effort for a single piece. This may also lead to a better utilization of the CPU caches, as smaller blocks of the input arrays are needed at once. After these preparations are done, all kernel invocations – one for each subpiece – are performed in parallel using OpenMP (8). Then, every node executes the undivider for each local subpiece (9) and bundles the local result using bundleResult (10). Every node transferres its bundle to the master (11), which restores the encapsulated result into the corresponding local piece and reverts its memory layout by calling unbundleResult (12). At last, all received pieces must be undivided (13) to ensure the user data corresponding to the root piece contains the whole result, which is now equal to the original, sequential result.

**Specialized Scheduler for Shared Memory** For an architecture with shared memory only, every thread is able to access the input data. Therefore, no communication and no bundling is needed. In-place access to the input data by the cores implies that memory layout optimizations are not performed, as they are tightly coupled with the bundling methods. However, a bundling and unbundling step may be used anyway to integrate a layout transformation, but this may lead to a performance degradation. In detail, on a shared memory system the scheduler first divides the root piece in at least as many subpieces as physical or logical cores are

available and invokes the localKernel once for each piece in multiple OpenMP threads. The third and last step then undivides all subpiecesafter the computation has been performed.

**Fall-Back Version for Purly Sequential Systems** If only one physical processor is available, the scheduler may use the purely sequential kernel to avoid any scheduling overhead. In that case the only required method is the serialKernel. Actually, the serial kernel does not need any DKU piece, only a pointer to the user data structure itself is passed to it.

## 4 DKU Framework

Work on the generator tool started with a prototypical implementation of a framework for the DKU pattern.

Besides the seven methods described in Section 2.5, this implementation of the DKU framework needs another one to generate all root pieces. Each root piece represents a new, independent computation, i.e., in the case of a matrix multiplication example several different multiplications can be specified and scheduled for execution at once. On the one hand, if the user code for DKU is generated automatically for a given loop nest, makeRootDKUPieces returns only a single root piece specifing exactly the whole input code. On the other hand, if the user code is modified or even completely written without the generator, the serialKernel may provide a version that is optimized on computing several instances at once.

All eight methods must then be introduced to the framework which is done by passing function pointers to a bunch of initialization methods. As this code is very generic, the generator encapsulates it in an initializer method to facilitate the use of the DKU framework.

The first version of the DKU framework was focused on debugging and, therefore, no parallel scheduler was included, i.e., all kernels were executed sequentially. In order to measure the speedup of the generated DKU code, the framework had to be adapted. The most important part of the modifications was to parallelize the scheduler, i.e., to enable it to execute all kernels in parallel. There are three ways to achieve this:

**OpenMP** First of all, the scheduler could be parallelized using OpenMP. This approach performs very well on a multicore shared memory architecture, as OpenMP has quite low overhead. But as this approach is completeley focused on shared memory, OpenMP provides no mechanism to transfer data using any kind of network.

**MPI** The Message Passing Interface (MPI) is a standardized approach to deal with distributed memory systems. MPI can handle both point-to-point and collective communication, but in the case of the DKU framework only low-level methods are needed, as the framework itself does not know anything about the data to transfer. Compared to OpenMP it has also a relatively high overhead. Combining both OpenMP and MPI is therefore a good choice to deal with clusters consisting of several multicore machines and to cover a large set of architectures.

MPI requires an initialization before it can be used (e.g. by calling MPI\_Init). And as the framework is designed to encapsulate even the decision which parallel language should be used, the initializer void DKU\_Init(int \*, char \*\*\*) must be invoked before parsing the program parameters and it calls MPI\_Init, if required. The framework also provides a method boolean DKU\_isMaster() to protect code that should be executed only by the master. This is required as all MPI nodes are started simultanously when launching the program. A delayed execution of arbitrary nodes is not possible. The presented method enables the user for example to ensure only the master reads or writes files from disk.

**GPGPU** Beside traditional shared and distributed memory systems, GPGPU is a fairly new domain in high-performance computing. The DKU framework can also be adapted to utilize the graphics processing units, if a CUDA<sup>1</sup> or OpenCL<sup>2</sup> kernel is available. Although this could lead to a higher performance, an automatic code generation for all DKU methods would be more complex and therefore only the composition of OpenMP and MPI was implemented.

**Layout Transformations** Another contribution is the extension of the DKU pattern by explicitly allowing memory layout transformations. In C, arrays are stored in row-major order, so accessing them row-wise would lead to a much smaller number of cache misses than accessing them column-wise. Consider, for example, the basic matrix muliplication from Figure 4.1. In contrast to the arrays A and C, B is accessed column-wise, which is more complex for the prefetcher to handle effectively. One possible solution to deal with this problem is to transpose matrix B. In general an additional rearranging of the memory layout is expensive and may exceed the speedup of the actual computation, but in the special case of using a distributed

<sup>&</sup>lt;sup>1</sup>Compute Unified Device Architecture (https://developer.nvidia.com/category/ zone/cuda-zone)

<sup>&</sup>lt;sup>2</sup> Open Computing Language (https://www.khronos.org/opencl/)

```

for (i = 0; i < r; ++i) {

1

for (j = 0; j < c; ++j) {

2

sum = 0;

3

for (k = 0; k < n; ++k) {

4

sum += A[i][k] * B[k][j];

5

}

6

C[i][j] = sum;

7

}

8

}

9

```

Figure 4.1: Matrix Multiplication Kernel

memory architecture all relevant input data must be transferred to the corresponding node. Therefore, the bundle method is called for each subpiece and all relevant data must be copied anyway, so applying layout transformations here can be done with relatively low overhead.

Beside the possible performance gain this extension also adds new constraints to the framework. First of all, as the bundle methods are optional, they may not be used on a shared memory system, which requires two different kernel methods – the standard in case of the original memory layout and another for the optimized one. The framework then chooses the appropriate version depending on the use of the bundle methods. Another constraint is that the master thread is the only one allowed to bundle the data and also at most once per call, because the layout transformation is tightly coupled with the bundling for performance reasons as aforementioned.

In addition to these explicit improvements the framework was cleaned up. All currently unnecessary preparations for future features were removed in order to reduce the overhead and enhance the readability.

### **5** Generator

The generator is both a software and a library to generate all DKU methods automatically, starting with a rather simple description of the input program. A brief description of the whole process when using the generator can be found in Chapter 3 and the following sections deliver a deeper insight in all mentioned parts, as well as the problems which came up during the development.

#### 5.1 Input Description

An early question of the project concerns the description of the algorithm that should be executed using the DKU framework. There are two different approches here. First of all, a very flexible one is to read a configuration file which contains all needed information. All parts of the polyhedral description, as for example, iteration domain or schedule, may be written in isl syntax and other parts like statement codes or variable definitions can be given as single C statements. A major disadvantage here is that the user must be capable of directly formulating the iteration domain and the schedule of all statements in isl syntax. This approach therefore has a high learning curce and it is rather error-prone.

Second, it is possible to parse a C source file that contains a sequential version of the algorithm that should be parallelized utilizing DKU. On the one hand, this enables the user to write a simple, sequential C code, which is easier for a programmer than the first approach. On the other hand, extracting a polyhedral representation is not as easy as simply parsing a complete polyhedral description, but there are different libraries to solve this problem. The one used in the generator is the polyhedral extraction tool (pet), which is introduced in Section 2.3.

As pet uses a real C compiler to parse the input file, it requires valid C99 source code. A simple input file for a matrix multiplication example is shown in Figure 5.1. The model extracted by pet is used to build the data structure for the generator, which is close to pet's representation. The generator can also be used as a library

```

void MM(int r, int c, int n,

1

float A[r][n], float B[n][c], float C[r][c]) {

2

3

float sum;

4

5

#pragma scop

6

for (int i = 0; i < r; ++i) {

7

for (int j = 0; j < c; ++j) {

8

sum = 0.0;

9

for (int k = 0; k < n; ++k)

10

sum += A[i][k] * B[k][j];

11

C[i][j] = sum;

12

}

13

}

14

#pragma endscop

15

}

16

```

Figure 5.1: Generator input for the matrix multiplication.

and its input can be created without pet. The internal data structure, which is created by the frontend consists of the following parts:

- **id** The DKU framework uses an id to distinguish different application codes. It is defined in the generator by either an optional argument, or it is derived from the filename of the sequential input code.

- **variables** This list contains all information about the used variables, as the generator has to insert code to declare them. In case of multi-dimensional arrays, the compiler needs beside the element type the extent of the outer dimensions to create code for computing the explicit memory address.

- **statements** Every statement is represented by an abstract syntax tree, which is similar to the representation pet uses.

- output This optional parameter can be used to define which arrays contain the result of the computation. If no output arrays are defined, the generated code collects and returns all modified data after the computation. In case of the matrix multiplication only the result matrix is bundled in the bundleResult method. But, if there are temporary arrays, whose elements are not needed by

the caller, they need not be transferred to the master and so the programmer may use the output parameter to specify this.

In addition to the file containing the input code, the user is also allowed to pass a second file containing a single isl map, which denotes layout transformations for all arrays. The frontend uses isl to parse the map and stores every transformation in the structure for the corresponding variable.

#### 5.2 Polyhedral Optimizations

**Dependence Analysis** Before any optimization or transformation can be found or applied, the generator needs to perform a dependence analysis. The dependencies describe an ordering between statement instances, which must not be interchanged in order to ensure the result of the program is still valid. A dependence analysis can be performed using the isl. It provides a method for computing dependencies, given sink and source access relations. Dependencies are called flow dependencies, if they denote from write accesses to a later read access of the same memory location and they can be computed by passing write accesses as sources and reads as sinks. Write accesses for both source and sink lead to so called output dependencies and an invocation with reads for the sources and writes for the sinks computes anti dependencies. All three types must be considered for all variables, because each of them involves a memory modification. Memory accesses can easily be aggregated in a single pass through all statements, as they are represented by isl relations within the abstract syntax trees.

In addition to the dependencies, this analysis also returns all sink accesses without any source access before. In case of computing flow dependencies, all elements that are read, but never written before according to the given read and write accesses, are also returned. The generator uses this information to determine which arrays contains input values and must therefore be transferred to the corresponding node.

**Scheduling** In order to use the DKU framework, at least the outermost loop of the resulting kernel code must be parallel. Therefore, the given description of the kernel code is passed to the isl scheduler in order to compute an optimal schedule. The scheduler integrated in isl uses an algorithm which is similar to Pluto's [BHRS08], but Feautrier's scheduling algorithm can be selected as well [Fea92].

```

void PP(int na, int nb, double A[na], double B[nb],

1

double C[na + nb - 1]) {

2

#pragma scop

4

for (int i = 0; i < na + nb - 1; i++)</pre>

S0: C[i] = 0.0;

6

for (int i = 0; i < na; i++)</pre>

8

for (int j = 0; j < nb; j++)</pre>

9

S1: C[i+j] += A[i] * B[j];

10

#pragma endscop

11

}

12

```

Figure 5.2: Generator input for the polynomial product.

Consider for example the input code from Figure 5.2. The extracted iteration domain and schedule are:

```

[na, nb] -> {

S0[i]: i>=0 and i<na+nb-1;

S1[i,j]: i>=0 and i<na and j>=0 and j<nb; }

[na, nb] -> { S0[i] -> [0,i,0]; S1[i,j] -> [1,i,j]; }

```

The original input does not contain an asynchronous parallelism, apart from the initialization of the result array C, because different iterations of both the i- and j-loops in lines 8 and 9 modify the same element of C. This can also be seen, when inspecting the computed dependencies, as there is a transition from S1 to itself for different values of the outermost loop iterator i:

```

[na, nb] -> {

S0[i] -> S1[0,i]: i>=0 and i<nb and na>0;

S0[i] -> S1[i+1-nb,nb-1]: i>=nb and i<na+nb-1 and nb>0;

S1[i,j] -> S1[i+1,j-1]: i>=0 and i<na-1 and j>0 and j<nb;}</pre>

```

A better schedule for this representation can be computed using isl:

[na, nb] -> { SO[i] -> SO[i,0,0]; S1[i,j] -> S1[i+j,i,1]; }

The iteration domain and the optimized schedule still describe the same computations, but the ordering of the statement instances may have changed. This reordering may help to exploit the parallelism of the computation. This new system can not be used directly to create the kernel code, as for the outer parallel dimensions, which now might exist, the generator must insert new structure parameters, which restrict the computation one kernel call has to perform. In order to be able to delimit individual dimensions, the generator creates a completely new system for the kernel code by applying the schedule to the iteration domain. This ensures every loop of the resulting kernel code corresponds to exactly one dimension of its iteration domain. The new iteration domain and the according schedule for the kernel is:

```

[na, nb] -> {

S0[i0,0,0]: i0>=0 and i0<na+nb-1;

S1[i0,i1,1]: i0>=0 and i0<na+nb-1

and i1>=0 and i1>i0-nb and i1<=i0 and i1<na; }

[na, nb] -> {

S0[i0,i1,i2] -> S0[i0,i1,i2];

S1[i0,i1,i2] -> S1[i0,i1,i2]; }

```

The dependencies for this new system can now be used to determine which dimensions can be executed in parallel (which is explained in the next paragraph):

```

[na, nb] -> {

S0[i0,0,0] -> S1[i0,0,1]: i0>=0 and i0<nb and na>0;

S0[i0,0,0] -> S1[i0,i0+nb-1,1]:

i0>=nb and i0<na+nb-1 and nb>0;

S1[i0,i1,1] -> S1[i0,i1+1,1]:

i1>=0 and i1>i0-nb and i1<na-1 and i1<i0; }</pre>

```

It is now possible to insert new structure parameters, which represent the new loop bounds in the resulting kernel code.

The final iteration domain and schedule for the kernel code are then:

```

[na,nb,_l0,_u0] -> {

S0[i0,0,0]: i0>=0 and i0>=_l0 and i0<na+nb+1 and i0<=_u0;

S_1[i0,i1,1]: i0>=0 and i0>=_l0 and i0<na+nb-1 and i0<=_u0

and i1>=0 and i1>i0-nb and i1<=i0 and i1<na; }

[na,nb,_l0,_u0] -> {

S0[i0, i1, i2] -> S0[i0, i1, i2]: nb+na>1;

S1[i0,i1,i2] -> S1[i0,i1,i2]: nb+na>1; }

```

```

if ((na >= 1) && (nb >= 1)) {

1

for (c1=max(0,_10);c1<=min(_u0,na+nb-2);c1++) {</pre>

2

S_0(c1, 0, 0);

3

for (c2=max(0,c1-nb+1);c2<=min(c1,na-1);c2++)</pre>

4

S_1(c1, c2, 1);

5

}

6

}

7

if (nb <= 0)

8

for (c1=max(0,_10);c1<=min(_u0,na+nb-2);c1++)</pre>

9

S_0(c1,0,0);

10

if (na <= 0)

11

for (c1=max(0,_10);c1<=min(_u0,na+nb-2);c1++)</pre>

12

S_0(c1, 0, 0);

13

```

Figure 5.3: Generated loop nest for kernel using the input as depicted in Figure 5.2.

The resulting loop nest generated by CLooG for this system is shown in Figure 5.3.

**Finding Parallelism** In a next step, the generator needs to know how many of the outer loops can be split by the divider, or in other words, the number of outer dimensions that do not carry any dependency. But to determine this, not all dependencies are relevant. Consider again the source code of Figure 5.1, the local variable sum is only used to avoid several accesses to the same element of array C, which may lead to a performance degradation, if the compilation updates the main memory on each access. But as it is the same variable for all iterations of the i and j loop, there is an anti dependency from line 12 to line 9 of the subsequent iteration for the outer loops. In a naive approach, this dependency prevents all parallelism, but as every kernel invocation has implicitly its own copy of all non-array variables, a shared update problem can not occur, so there is no problem if such dependencies are violated. Therefore, when computing the number of parallel dimensions, anti or output dependencies for non-array variables must not be considered, as only flow dependencies carry information.

Another problem is that the optimized schedule may contain constant dimensions that do not map to an explicit loop of the resulting kernel code, but only effect the structure of the loop nest, as mentioned in Section 2.3 and depicted in Figure 2.3. Therefore the generator categorizes each dimension as follows:

```

Input: Dependency deps[n_dims]

1

Result: Category dims[n_dims]

2

3

for (int i = 0; i < n_dims; ++i)</pre>

4

dims[i] = parallel_scalar;

5

6

for (Dependency dep : deps) {

7

for (int i = 0; i < n_dims; ++i) {</pre>

8

if (dims[i] == parallel_scalar

9

&& Is_no_scalar_dimension(dep, i))

10

dims[i] = parallel_loop;

11

12

if (Dependency_is_carried_by_dimension(dep, i))

13

dims[i] = sequential;

14

}

15

}

16

```

Figure 5.4: Computation of the category for each dimension.

- **parallel loop** Determines that this dimension describes a loop of the resulting kernel code and it can be executed in parallel. Therefore the divider is allowed to split it.

- **parallel scalar** These dimensions are not represented directly in the generated code, as they refer to constant output dimensions of the computed schedule, which are explained in Section 2.3, but they do not limit the parallelism. They must not be considered by the divider.

- **sequential** For sequential dimensions it does not matter if they are represented in the resulting kernel code by a loop, as they carry a dependence. Therefore neither these, nor any of the following dimensions are allowed to be split by the divider.

Figure 5.4 shows an algorithm for the categorization of all dimensions, given all dependencies. In detail, Is\_no\_scalar\_dimension(dep, i) is true, if at least domain or range of dimension i from the dependency dep is not a constant value. Dependency\_is\_carried\_by\_dimension(dep, i) returns true, if dimension number i carries the given dependency dep.

**Definition 2 (loop-carried dependency)** A loop or dimension i carries a dependency iff the *i*th element of the distance vector for the dependency is non-zero and all previous i - 1 elements are zero.

The distance vector is simply the difference between the target iteration vector and the source iteration vector of the dependency.

The actual number of outer parallel dimensions and also the number of dimensions the divider is allowed to split can now easily be determined by counting all *parallel\_loop* entries of the computed category array that appear before any *sequential* entry.

# 5.3 Layout Transformation

As already mentioned in Section 4, layout transformations may increase the performance of the application code on distributed memory systems and can be realized with almost no overhead, as the input data must be copied anyway. But the computation of an optimal transformation for a given application code is not trivial.

This section presents a new idea for computing an affine layout transformation for a given program. The core part of this approach is to use an unmodified scheduling algorithm to compute the transformation. Both scheduling algorithms implemented in isl require two different types of dependencies:

validity The computed schedule is guaranteed to respect all validity dependencies.

**proximity** The second input consists of proximity constraints and the algorithm tries to minimize the dependence distances over them.

If the scheduling algorithm is used to compute a layout transformation, there are no hard constraints on the order of the elements and therefore there are no validity dependencies, the algorithm must consider. But the minimization part for proximity dependencies of the scheduling algorithm can be used to minimize the distance between subsequently used array elements.

As the layout transformation is used to optimize the cache utilization, the distance between subsequent accesses to an array must be minimized. A relation over array elements that indicates for every value the element that is accessed consecutively when executing the kernel can be used as a proximity dependence relation.

The computation of these proximity dependencies starts with the access relations for a given array and a polyhedral representation of the kernel code. Consider for example the matrix multiplication from Figure 5.1, if the statement in line 11 is named S, the access relation for array B can be denoted as:

In a next step, new access relations are computed by removing all array dimensions. The resulting relation then represents accesses to the whole array. For the access to array B, the modified relation could be:

Then a flow dependence analysis is performed, using the newly created access relation for both source and sink. For the given example, the schedule of the source code of Figure 5.1 is simply an identity map, so the computed dependencies are:

```

[r,c,n] -> {

S[i,j,k] -> S[i,j,k+1] : 0<=i<r and 0<=j<c and 0<=k<n-1;

S[i,j,n-1] -> S[i,j+1,0] : 0<=i<r and 0<=j<c-1 and n>=1;

S[i,c-1,n-1] -> S[i+1,0,0] : 0<=i<r-1 and n>=1 and c>=1; }

```

These dependencies now denote for every statement instance that accesses the given array, the subsequent instance under the given schedule, which also accesses the same array. A last step is now to transfer both domain and range from the iteration space to the index space of the appropriate array. This can be done by simply applying the original access relation to both domain and range of the dependence maps. For the matrix multiplication example this would lead to the following proximity dependencies:

```

[r,c,n] -> {

B[k,j] -> B[k+1,j] : 0<=k<n-1 and 0<=j<c and r>=1;

B[n-1,j] -> B[0,j+1] : 0<=j<c-1 and r>=1 and n>=1;

B[n-1,c-1] -> B[0,0] : r>=2 and n>=1 and c>=1; }

```

It is easy to verify that the source code from Figure 5.1 accesses the elements of array B in the same ordering as denoted by the dependencies.

In theory, the scheduler should now return an optimal layout transformation for the appropriate array, as it minimizes the distance between subsequent array accesses. But the actual output is in most cases an identity, as the given proximity constraints apear to be too complex for the scheduling algorithm. There are two approaches which might solve this problem. On the one hand, a heuristic can be used to preprocess and simplify the computed dependencies. On the other hand, the scheduling algorithm can be adapted to this problem. The first approach was tested in this work and the adaption of the algorithm remain as future work. Following the example above, the first two mentioned maps contain multiple elements and therefore they describe multiple different dependencies, depending on the value of the structure parameters n and c. In contrast to this, the third map only contains a single element, which leads to a single dependency, namley from the last element of the matrix B to the first one. So the last map can be considered as less important for the layout transformation. Removing it and invoking the isl scheduler then results in the desired transformation:

[c,n,r] -> { B[k,j] -> B[j,k]; }

A filter for the dependencies, which removes maps, that contain only a single element is implemented, but this is only sufficient for rather simple input codes, as e.g. the matrix multiplication. With an increasing complexity of the input, the requirements for the preprocessing heuristic are also growing and a universal solution could not be found.

In contrast to this, specializing the scheduler is more extensive, but it may lead to more satisfactory results for a larger number of programs.

## 5.4 Code Generation

For the code generation part, two different approaches are possible, the *templated* generation and the *transformer generation*.

On the one hand, the application code could be created by using a template. That means, the application code is derived from a generalized code file, called template. The template is then modified at previously marked positions to adapt it according to the given model. An advantage of this apporach is that the template can be basically read and understand without inspecting the source code of the generator, but the use of a template needs the generator to be able to parse it in order to find and replace all marks.

On the other hand, a more lightweight and more flexible approach is to use a transformer. That means, the generator writes the complete application code di-

rectly into the output file and therefore it handles a huge amount of strings. Structural modifications of the generated code also require a recompilation of the whole generator and in contrast to a template file, the inspection of the basic structure results in studying the source code, or the generated files for different inputs. But as the transformer is easy to integrate and it does not need additional external libraries, this approach was chosen for the generator.

### 5.4.1 Divider / Undivider

The divider's task is to split the input piece in as many subpleces as desired, in a way that every subpleces leads to an almost identical amount of work for the kernel. It is allowed to create more or fewer subpleces as requested, but to optimally exploit the hardware, the given number should be respected.

**Distribution of Subpieces accross parallel Dimensions** In case of multiple parallel loops, the computation can be split in more than one dimension. This may lead to problems if the requested number of subpieces is prime. Using a consistent distribution, i.e. splitting the iteration domain using hyperplanes, the only possibility to respect the given number is to split only a single dimension. This could be a waste of parallelism potential, as splitting multiple dimensions also lead to an indirect tiling of the computation. Consider again the matrix multiplication example from Figure 2.1a, the outer  $\pm$  loop iterates over all rows and the  $\pm$  loop traverses the columns of the result matrix. If only the first dimension is split by the divider, each of the resulting subpleses tranverses the array B multiple times with the maximum possible reuse distance. That means, before a specific element of the matrix is accessed the second time, all others are required first. The CPU cache can now only increase the performance if the whole matrix B can be cached at once. If the divider now splits both the i and the j loop, each subpiece requires only a subset of the array B. This leads to a smaller reuse distance, which may increase the performance, if all accessed data can be cached now.

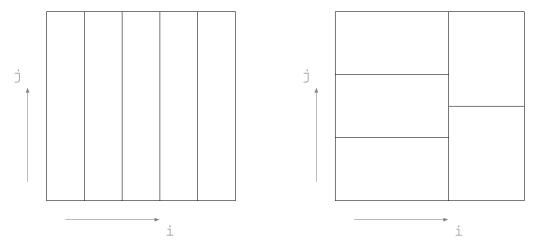

Consider an application with two parallel loops that should be split in five subpieces. Figure 5.5a shows a naive partitioning of both dimensions. It can easily be seen that all subpieces cover the same area, but this solution does not exploit the second parallel dimension *j*. A better partitioning for the same problem is shown in Figure 5.5b. This can be achieved by dropping the constraint that each dimension has to be split evenly by using hyperplanes, for one single dimension. Furthermore

- (a) If all dimensions must be split evenly by hyperplanes, the only partitioning possible does not exploit both dimensions, as the requested number only has the trivial factorization  $5 \cdot 1$ .

- (b) If a single dimension is allowed to be split arbitrarily (here dimension j), a better partitioning is possible.

- Figure 5.5: Possible partitioning with five subpleces created by the divider for a two dimensional iteration space.

```

Inputs: n, d

1

Results: c_i, b

2

3

remaining = n;

4

prod = 1;

5

6

for i = 0...d-2 {

7

root = round ( \sqrt[d-i]{remaining + \frac{1}{4}} );

8

remaining = \frac{\text{remaining}}{\text{root}};

9

root

c_i = \text{root};

10

prod = prod · root;

11

}

12

13

c_{d-1} = remaining;

14

prod = prod · remaining;

15

b = n - \text{prod};

16

```

Figure 5.6: Algorithm used to compute the number of bars  $c_i$  per dimension.

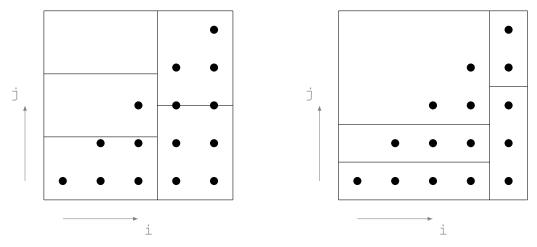

(a) subpieces created independently from (b) optimal loop bounds for the subpieces according to the iteration domain

Figure 5.7: Illustration of five subpieces for the code from Figure 2.1a.

it is possible for an arbitrary dimensionality  $d \in \mathbb{N}$  to find a  $k \in \mathbb{N}$  and a partitioning of the iteration domain into  $n \in \mathbb{N}$  subpleces such that all except one dimension are divided into either k or k + 1 blocks and for the last dimension all blocks are also divided into either k or k + 1 pieces. This can be formulated as follows:

#### **Conjecture 1**

$\forall n, d \in \mathbb{N} : \exists k \in \mathbb{N} : \exists c_0, \dots, c_{d-2} \in \{k, k+1\} : k \cdot \prod_{i=0}^{d-2} c_i \le n \le (k+1) \cdot \prod_{i=0}^{d-2} c_i$

The procedure used to compute such a partitioning is shown in Figure 5.6. Its correctness is not proven mathematically, but was tested empirically for all combinations of  $n \in \{1, ..., 1.000.000\}$  and  $d \in \{1, ..., 100\}$ . The summand  $\frac{1}{4}$  inside the root in line 8 is required to ensure the computed  $c_i$  have the desired form. The results  $c_0, ..., c_{d-2}$  determine the number of blocks the first d - 2 dimensions are split into. All these blocks are then divided into k or k + 1 pieces, such that overall n pieces are available.

**Shape and Size of the Subpieces** Another problem appears at the explicit subpiece creation. The given code only computes the layout of the subpieces, but their explicit shape and size must be determined in a second step. Consider again the source code from Figure 2.1a, a naive creation of the subpieces is shown in Figure 5.7a. It can easily be seen that this does not lead to an appropriate load balance, as for example the upper left subpiece does not contain any computation. Therefore, it is advisable to shift the subpiece boundaries in order to balance the number of statement instances inside them. Figure 5.7b shows an optimal partitioning of the given iteration domain. It can be determined by performing a binary search and the generator is able to create code for this part. In detail, let  $\rho(p)$  be the number of integral points inside the iteration domain of the kernel description, which is encapsulated in the subpiece p. The generator uses barvinok [VSB<sup>+</sup>07], a library which extends isl, to compute a C expression for  $\rho$ . The subpieces  $p_1, ..., p_n$  then denote an optimal partitioning of the parent piece p, if  $\rho(p_1) \approx ... \approx \rho(p_n) \approx \frac{\rho(p)}{n}$ . The best loop bounds for a subpiece  $p_i$  can be computed by evaluating  $\rho(p_i)$  and comparing it to the desired  $\frac{\rho(p)}{n}$ . If the number of iterations matches, an optimal piece was found, if its too small or too large, the size must be adapted accordingly and tested again. As Figure 5.7b shows, it is in general not possible to find a perfect solution, for which all subpieces are exactly equally sized, because the subpieces are restricted to a rectangular shape. But in practice, if the overall number of iterations is large enough, its impact is quite low.

In contrast to the rather complex divider code, the undivider only has to free the subpiece structure. As the divider does not copy the user data for the subpiece creation, but only references the same structure the original piece contains, the undivider does not need to collect any data for the result.

### 5.4.2 Bundle / Unbundle

**General Specification** The main specification for the bundle code is to create a single memory block that contains all data which must be transferred to other nodes. But, as communication and memory transfers produce a huge overhead, another important part for the bundle methods is to limit it as good as possible.

**Communication Reduction** A fist obvious improvement is to transfer not all arrays entirely to every node, but only the part the corresponding node requires in order to compute its subpiece. The information which array and even what specific elements a single node requires to compute its part can be extracted from the results of the dependence analysis, as suggested in Section 5.2. The flow dependence analysis isl provides, requires in general three different relations, a schedule, which indicates at which specific virtual point in time the statement instance is executed and two maps that indicates source and sink access relations to an arbitrary domain. In addition to the dependencies, the used algorithm computes a relation no\_source, which maps each point p of the given domain to the according target

*t*, which is specified by the sink access, if no chronological previous – according to the given schedule – point *q* exists, that reads the same target *t*, as indicated by the source relation. Applying this mapping to the iteration domain of the kernel description results in a set, describing only the array elements that has to be transferred.

The most aggressive reduction of the communication volume can then be realized by simply using the created set as an iteration domain for a new loop nest, which can easily be generated utilizing CLooG. The loop nest now scans only the needed array elements and therefore the body of this loops must simply copy the element at the index denoted by the iteration vector to the next empty slot of the bundle. In order to allocate enough memory for the bundle, the number of elements for all arrays can be computed by counting all integral points inside the corresponding isl set using barvinok. The same code may also be used to extract the bundle inside the unbundleInput method.

A similar optimization can also be performed for the results bundle. As the unbundleResults method only has to extract the computed results in order to ensure data from other nodes is not overwritten, all information needed to optimize the communication volume has to be computed anyway. This information can easily be determined by collecting all access relations that represent only array modifications, and applying them to the iteration domain of the kernel representation. The resulting set now represents all array elements, computed for a given subpiece description. The loop code for both bundleResults and unbundleResults can then be generated analogous to bundleInput and unbundleInput respectively.

**Memory Reuse** Another rather simple possibility to reduce the overhead of the memory transfers is to reuse the bundle memory. Therefore, the unbundleInput method neither need to allocate new memory for the input data nor extract the bundle explicitly. The only task left is to compute the positions of all input arrays inside the bundle memory and to store the corresponding pointer in the piece structure.

If the whole input is transmitted to the nodes, the offset calculation is quite simple, as only the complete size of every input array must be known and this information is part of the input description.