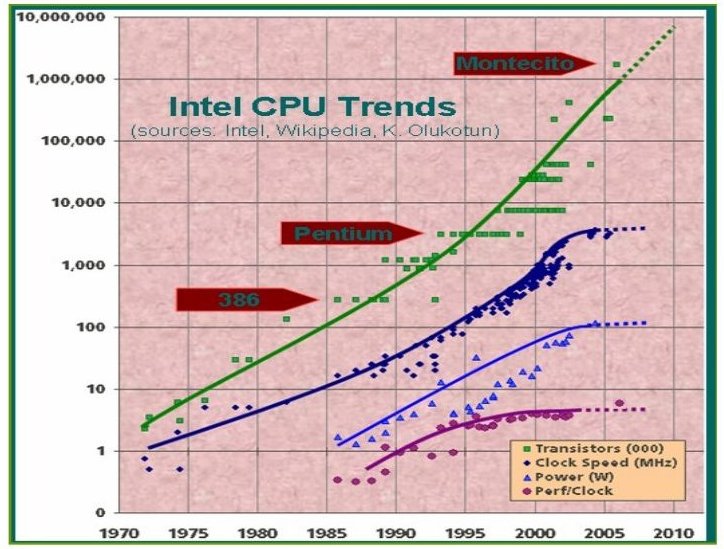

Bisher hat jede neue Auflage von Prozessorchips Leistungsverbesserungen

gebracht. In Zukunft wird dies nur noch durch eine Erhöhung der Prozessorenzahl

möglich sein, denn die Leistung einzelner Prozessoren kann nicht mehr weiter

verbessert werden. Die nebenstehende Abbildung zeigt, dass bei ungebremster

Steigerung der Packungsdichte der Transistoren auf dem Chip (Kurve

"Transistors") die Taktrate (Kurve "Clock Speed") abflacht. Eine Steigerung

der Taktrate führt auch kaum noch zu einer Leistungssteigerung (Kurve

"Perf/Clock"). Die Entwicklung des Stromverbrauchs (Kurve "Power") macht

gleichzeitig eine weitere Motivation zum Übergang vom sequenziellen zum

parallelen Rechnermodell deutlich: Bei vergleichbarer Rechenleistung ist

Parallelität umweltfreundlicher!

Bisher hat jede neue Auflage von Prozessorchips Leistungsverbesserungen

gebracht. In Zukunft wird dies nur noch durch eine Erhöhung der Prozessorenzahl

möglich sein, denn die Leistung einzelner Prozessoren kann nicht mehr weiter

verbessert werden. Die nebenstehende Abbildung zeigt, dass bei ungebremster

Steigerung der Packungsdichte der Transistoren auf dem Chip (Kurve

"Transistors") die Taktrate (Kurve "Clock Speed") abflacht. Eine Steigerung

der Taktrate führt auch kaum noch zu einer Leistungssteigerung (Kurve

"Perf/Clock"). Die Entwicklung des Stromverbrauchs (Kurve "Power") macht

gleichzeitig eine weitere Motivation zum Übergang vom sequenziellen zum

parallelen Rechnermodell deutlich: Bei vergleichbarer Rechenleistung ist

Parallelität umweltfreundlicher!

Daher enthalten Rechner neuerdings mehrere Prozessoren (sog. Kerne): z.Zt. bis zu acht, in naher Zukunft Dutzende, in etwas fernerer Zukunft noch mehr. Aktuelle Beispiele sind der 6-Kernchip Dunnington von Intel oder 8-Kernchip Niagara2 von Sun, aber es gibt auch bereits einen Chip mit 80 Kernen (den Polaris von Intel) und sogar einen mit 192 Kernen (den Metro von Cisco). Eine andere Quelle von sogar noch leistungsfähigerer Parallelität sind die Grafikprozessoren, z.B. von NVIDIA oder AMD. Am bekanntesten ist hier wohl der IBM Cellprozessor.

Damit wird das Problem der Programmierung derartiger Rechner (Parallelprogrammierung) von einem Nischenthema zu einer zentralen Herausforderung an die Software-Technologie. Dual- und Quadcores lassen sich noch effektiv betreiben, indem man die aktivsten Prozesse von Anwendungen und Betriebssystem auf die einzelnen Prozessoren verteilt - eine Aufgabe, die von der Software-Industrie gelöst werden kann. Spätestens bei acht Kernen wird dieses Vorgehen aber nicht mehr ausreichen, da die Zahl der verfügbaren Prozessoren die Zahl der i.d.R. aktiven Prozesse übersteigen wird. Um nicht Prozessoren brach liegen zu lassen, müssen Mittel gefunden werden, sie sinnvoll einzusetzen.

Ideen, wie dies geschehen kann, sind reichlich vorhanden. Sequenzielle Prozesse können aufgespalten, d.h. parallelisiert werden, sofern die Abhängigkeiten im Prozess dies zulassen. Prozesse können auf mehreren Prozessoren dupliziert oder variiert ablaufen, um die Ausfallsicherheit zu erhöhen. Analyse- und Wartungsprozesse können hinzugefügt werden, um den Programmablauf zusätzlich zu überwachen, zu verwalten und zu optimieren. Zur Umsetzung dieser Ideen sind Techniken gefragt, die gegenwärtig noch nicht marktfähig, gerade einmal angedacht oder noch überhaupt nicht erkannt sind.

Bei der Nutzung von Multicores gehört Parallelität i.d.R. nicht zur Problemstellung, sondern wird als Merkmal der Lösung angeboten. Sie ist kein notwendiges Mittel zur Lösung des Rechenproblems, sondern ein Optimierungsmittel. Folglich kann sie frei gestaltet werden, solange die Abhängigkeiten im Lösungsprozess gewahrt bleiben und die Multicore-Hardware in geeigneter Weise angesprochen wird. Parallelität kann in vielen Formen auftreten: statisch vorhersagbar oder sich dynamisch entwickelnd und verändernd, strukturiert oder unstrukturiert, grobkörnig oder feinkörnig - je nach Anwendung.

Dieses Seminar wird sich mit einigen Aspekten dieser Herausforderung beschäftigen. Es gliedert sich in die folgenden Themengebiete:

| Termin | Thema | Vortragende(r) | Ausarbeitung | Folien | Anhänge |

|---|---|---|---|---|---|

| 30.04. | Multicore-Architekturen | Philipp Wendler | Wendler Handout | Wendler Folien | |

| 07.05. | Transaktionsspeicher | Christian Vaitl | Vaitl Handout | Vaitl Folien | |

| 28.05. | OpenMP und MPI für Multicore | Cheng Xu | Xu Handout | Xu Folien | |

| 04.06. | GPU-Programmierung: OpenCL | Markus Hauschild | Hauschild Handout | Hauschild Folien | |

| 25.06. | Spekulation auf Fadenebene | Edgar Kalkowski | Kalkowski Handout | Kalkowski Folien | |

| 02.07. | Die Sprache Hydra | Stefan Zwicklbauer | Zwicklbauer Handout | Zwicklbauer Folien | |

| 09.07. | Die Sprache X10 | Alexander von Rhein | von Rhein Handout | von Rhein Folien | |

| 16.07. | Multithreading mit Pthreads | David Kalftenegger | Klaftenegger Handout | Klaftenegger Folien | Klaftenegger Beispiele |

| 23.07. | Die Sprache Chapel | Andreas Simbürger | Simbürger Handout | Simbürger Folien | Simbürger Beispiele, Simbürger Comic |